CMOS逻辑IC基础知识_cmos逻辑门电路原理图

目录:

1.cmos逻辑门电路分析

2.cmos逻辑门的一般结构图

3.cmos门电路逻辑功能

4.cmos逻辑门电路怎么看写表达式

5.cmos门电路的逻辑功能测试小结

6.cmos逻辑门是什么极型门电路

7.cmos构成逻辑门

8.cmos电路逻辑功能

9.cmos逻辑电路的两种基本模块

10.cmos逻辑电路的特点

1.cmos逻辑门电路分析

CMOS逻辑IC基础知识 老王卖瓜:芯片测试原理及实践CMOS逻辑IC基础知识 | 东芝半导体&存储产品中国官网第Ⅰ章:CMOS逻辑IC概述 什么是逻辑IC?

2.cmos逻辑门的一般结构图

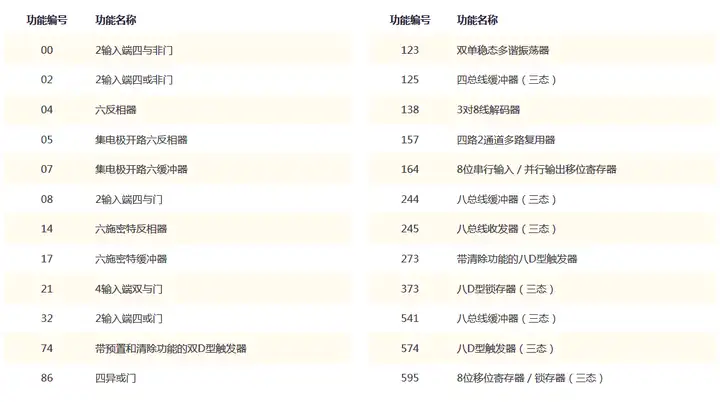

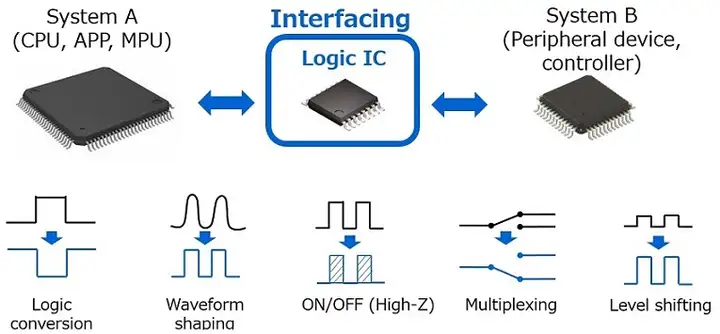

逻辑IC是一种对一个或多个数字输入信号(由1和0或H和L表示)执行基本逻辑运算以产生数字输出信号的半导体器件。连接或断开模拟信传导路径的模拟开关也被归类为逻辑IC。

3.cmos门电路逻辑功能

什么是标准逻辑IC? 多个制造商都可以提供基本逻辑门作为行业标准IC,它们在功能和引脚上均兼容 这些IC被称为标准逻辑IC除了一些小封装之外,不同制造商的标准逻辑IC都采用引脚兼容的封装。

4.cmos逻辑门电路怎么看写表达式

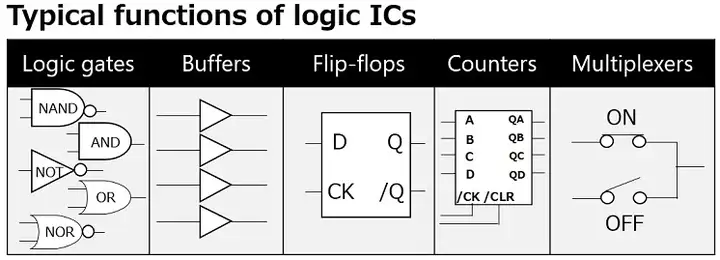

具有相同功能编号的标准逻辑IC提供相同的功能和引脚分配。

5.cmos门电路的逻辑功能测试小结

【参考:典型标准逻辑IC的功能编号】标准逻辑IC的功能编号根据功能、电路数量、输入逻辑和输出逻辑进行预定义。

6.cmos逻辑门是什么极型门电路

标准逻辑IC的类型 标准逻辑IC根据其结构(即使用的制造工艺)分为以下具有不同电气特性的类型目前最为常用的是就兼具低功耗和低成本特点的CMOS逻辑IC■TTL(晶体管-晶体管逻辑)。

7.cmos构成逻辑门

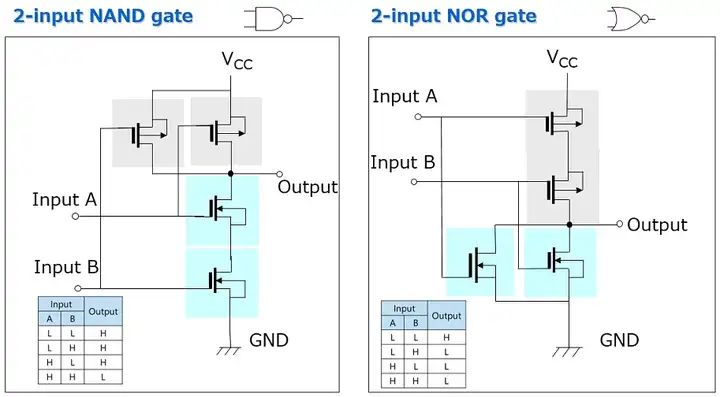

最初被广泛用作标准逻辑IC的双极逻辑相比CMOS逻辑IC,提供更高的电流驱动能力和运行速度,但消耗更多的功率■CMOS逻辑(CMOS:互补MOSFET)结合p沟道和n沟道MOSFET,实现比TTL更低的功耗

8.cmos电路逻辑功能

最初比TTL慢,但由于精细的晶圆制造工艺,现在提供比TTL更高的运行速度■BiCMOS逻辑(双极CMOS)输入级和逻辑电路采用CMOS工艺以降低功耗,输出级采用双极晶体管以提高电流驱动能力MOS双极组合制造工艺复杂,成本高

9.cmos逻辑电路的两种基本模块

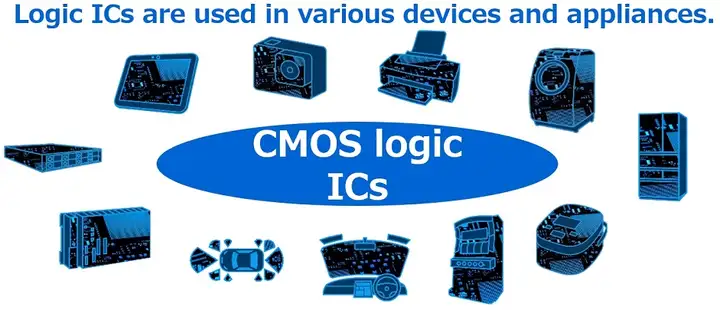

使用CMOS逻辑IC的设备 过去,CMOS逻辑IC在实现主要系统功能方面发挥了重要作用但是现在外围部件被集成到LSI芯片中,改进了以改善功能并缩小了电气和电子应用的规模即便如此,CMOS逻辑IC在各种应用中仍然是不可或缺的,因为它们是连接不同LSI芯片和电路板的粘合逻辑。

10.cmos逻辑电路的特点

使用CMOS逻辑IC的原因 逻辑IC用于连接不同的LSI芯片和电路板它们还用于对逻辑电路进行微小的修改和调整,例如增加信号驱动能力(即缓冲信号)、塑造信号波形、调整信号输出时序以及对系统进行较小的更改。

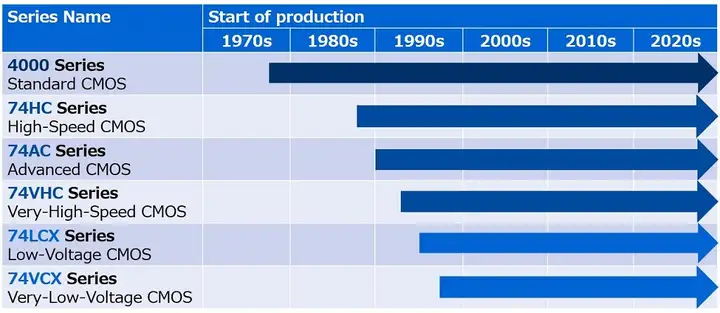

CMOS逻辑IC分类及各系列概述 自推出第一个标准CMOS系列(4000系列)以来,东芝已经发布了连续几代高速和低压CMOS逻辑IC。

东芝继续提供适用于各种应用,宽工作电压范围(1.2V至18 V)的CMOS逻辑IC。常见问题:通用逻辑IC系列之间有什么区别?

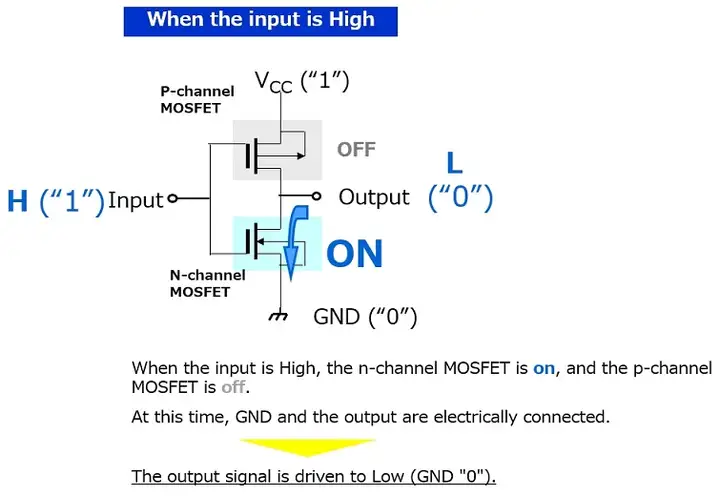

第Ⅱ章:CMOS逻辑IC基本操作 什么是CMOS逻辑IC? 使用互补的p沟道和n沟道MOSFET对的电路称为CMOS(互补MOS)CMOS逻辑IC以各种方式组合MOSFET来实现逻辑功能。

由一对p沟道和n沟道MOSFET组成的逻辑门称为反相器。

以下简要介绍反相器的操作。

通过组合p沟道和n沟道MOSFET可以实现各种逻辑功能。

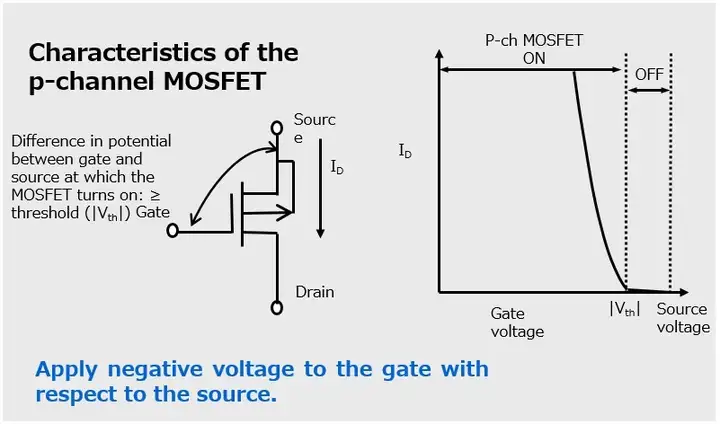

CMOS逻辑IC基本操作 当MOSFET的栅极-源极电压超过某个电压(阈值电压,|Vth|)时,漏极-源极电阻减小,使得MOSFET导通这种漏极-源极电阻称为导通电阻n沟道和p沟道MOSFET的栅极和源极之间施加的电压方向不同。

下图显示了MOSFET导通的条件 N沟道MOSFET:当栅极电压比源极电压高|Vth|时,n沟道MOSFET导通。

P沟道MOSFET:当栅极电压比源极电压低|Vth|时,p沟道MOSFET导通。

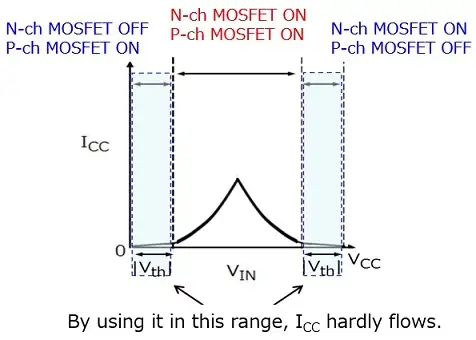

下图显示了反相器,它是CMOS逻辑IC的基本组成部分当VIN处于VCC或GND电平时,p沟道或n沟道MOSFET均关断因此,VCC和GND之间只有很小的电流(ICC)流过当输入处于稳定状态时(处于VCC或GND电平),ICC非常低。

CMOS逻辑IC(反相器)的组件下图显示了CMOS的VIN-ICC曲线当VIN介于0和|Vth|之间或VCC-|Vth|和VCC之间时,VCC和GND之间只有很小的电流(ICC)流过但是,当VIN介于|Vth|和VCC-|Vth|之间时,直通电流从p沟道MOSFET到n沟道MOSFET,从而增加了ICC。

因此,应注意确保避免对于VIN的输入变化过慢

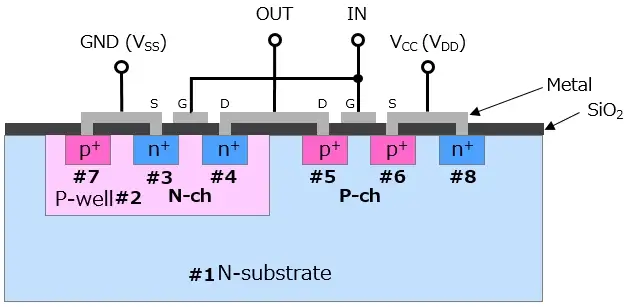

CMOS逻辑IC的VIN-ICC曲线CMOS逻辑IC基本配置 CMOS逻辑IC的横截面示例在n基底上形成宽的扩散区(p阱)在p阱上形成n沟道MOSFET在n基底上形成p沟道MOSFET。

具体取决于工艺,在p基底上形成n阱由于MOSFET的性能和集成密度由栅极宽度决定,所以制造工艺将用栅极宽度来表示例如,栅极宽度为1.0μm的CMOS工艺称为1.0μm CMOS工艺(在本例中,栅极宽度是指#3和#4之间以及#5和#6之间的距离。

)

#1.N基底:通常是晶圆基底#2.P阱:形成n沟道MOSEFT的区域#3.n沟道MOSFET源极的扩散区#4.n沟道MOSFET漏极的扩散区#5.p沟道MOSFET漏极的扩散区#6.p沟道MOSFET源极的扩散区

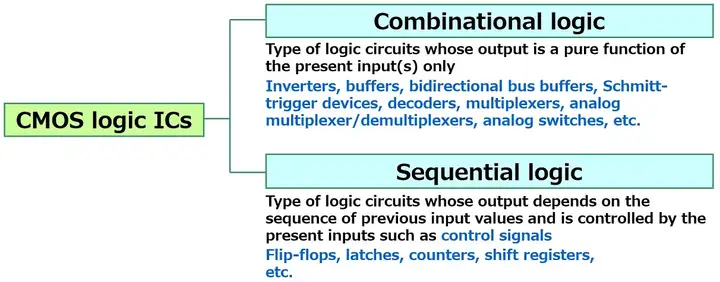

#7.p阱偏压扩散区#8.n基底偏压扩散区第Ⅲ章:CMOS逻辑IC基础知识 CMOS逻辑IC基础知识 CMOS逻辑IC大致分为组合逻辑和时序逻辑。本节介绍主要的逻辑电路。

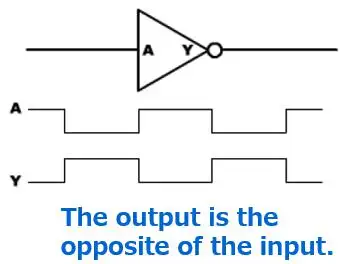

组合逻辑:反相器和缓冲器 反相器举例:74VHC04 反相器是一种输出(Y)与输入(A)相反的逻辑门。

逆变器的操作(示例:VHC04)缓冲器举例:74VHC244 缓冲器是一种用于增加驱动能力以增加扇出数或信号速度的逻辑门。缓冲器不执行任何逻辑操作。它还帮助调整信号的波形。

缓冲器的操作(示例:VHC244)双向总线缓冲器(收发器)示例:74VHC245双向总线缓冲器(收发器)是一种其I/O引脚可配置为输入和输出以接收和发送数据的逻辑电路由于收发器允许通过控制信号(DIR)更改信号方向,所以它沿着总线传输,双向传输数据。

以下显示了收发器的应用示例。如果是双向总线信号,则通过电阻将总线的输入和输出连接到VCC或GND。在这种情况下,应注意确保输出不短路。

双向总线缓冲器的应用示例通过在/G为高电平时更改DIR的值,可以轻松更改A和B引脚的方向。

/G为高电平时,更改DIR的值和外部数据的方向 在周期#0,数据从B传输到A 在周期#1,A引脚处于高Z状态因此,输出数据无效 在周期#2,更改DIR的值和外部数据的方向 在周期#3,启用A和B引脚然后,输出数据在周期#4开始时保持稳定。

在周期#4,数据从A传输到B组合逻辑:施密特触发装置 施密特触发装置示例:VHC14 施密特触发装置在两个输入阈值电压之间有一个磁滞带下面显示了具有输入阈值滞后的施密特反相器的输入和输出波形。

对于具有磁滞的IC,正向阈值电压(VP)不同于负向阈值电压(VN)对于缓慢上升或下降的输入,输入阈值滞后(VH)有助于稳定输出即使存在输入噪声或电源或噪声引起的接地反弹的情况下,IC也不会产生错误输出,除非噪声或反弹超过磁滞宽度。

施密特反相器

施密特反相器的输入和输出波形组合逻辑:解码器 解码器示例:VHC138解码器将N个编码输入的二进制信息转换为最多2N个独特输出它通常用于增加端口数量和生成芯片选择信号解码器的操作。

以下显示了3对8解码器(即具有三个输入和八个输出的解码器)的逻辑符号、真值表和时序图。

3对8解码器的逻辑符号和真值表

3对8解码器的时序图下面显示如何使用3对8解码器从三个输入(A、B和C)生成八个芯片选择信号当A、B和C都为低电平时,只有/Y0输出提供逻辑低电平,所以选择IC0此图表明,通过三个输入的组合,可以从最多八个芯片中选择任意芯片。

3至8解码器的时序图组合逻辑:多路复用器 多路复用器示例:74VHC157, 74VHC153 多路复用器将从多个输入信号中选择一个信号并将其转发到单个输出线。

2对1多路复用器的逻辑符号和真值表下面的时序图显示了如何从两个输入中选择一个信号。当选择引脚为低电平(0)时,信号从A引脚转发到Y引脚。当选择引脚为高电平(1)时,信号从B引脚转发到Y引脚。

2对1多路复用器的时序图多路复用器示例

组合逻辑:模拟多路复用器/解复用器 模拟多路复用器/解复用器示例:74VHC4051,74VHC4052,74VHC4053 模拟多路复用器包含模拟开关(见下一页),以从多个模拟输入中选择一个信号并将其转发到单个输出线。

由于模拟开关可以双向传输信号,因此模拟多路复用器也可用作解复用器

模拟多路复用器/解复用器可用于传输模拟和数字信号组合逻辑:模拟开关 模拟开关示例:74VHC4066 模拟开关可以在任一方向上传导正弦波信号等模拟信号它在打开时传递信号,在关闭时阻断信号模拟开关由一对n沟道和p沟道MOSFET并联组成,以降低导通电阻,提高I/O线性特性。

模拟开关的数据表显示了典型的正弦波失真、最大频率响应、馈通衰减、串扰和其它模拟开关特性。以下是模拟开关的逻辑符号、真值表、时序图和逻辑示意图。

模拟开关的逻辑符号和真值表

模拟开关的时序图

模拟开关的逻辑示意图时序逻辑:锁存器 锁存器示例:74VHC373 锁存器可以在特定条件下保留数据锁存器有D型和RS(复位和设置)型等类型下面将以D型锁存器为例对操作进行说明例如,D型锁存器具有输入数据引脚(D)、锁存器启用引脚(LE)和输出数据引脚(Q)。

在此例中,当LE为低电平时,Q将保留D的先前值当LE为高电平时,Q将跟随D而变化下面显示了D型锁存器的时序图

D型锁存器的逻辑符号和真值表

D型锁存器的逻辑示意图

D型锁存器的时序图时序逻辑:触发器 触发器示例:74VHC74 触发器可以在特定条件下保留数据“flip-flop”(触发器)这个词有时缩写为FF触发器有D型和JK型等类型下面将以D型触发器为例对操作进行说明。

D型触发器与D型锁存器的不同之处在于,即使在时钟设置为无效后(在本例中为低电平)之后,D型触发器仍保留输出数据(当LE输入为高电平时,D型锁存器将数据从D输入端传输至Q输出端)例如,D型触发器具有输入数据引脚(D)、时钟引脚(CK)和输出数据引脚(Q)。

该触发器将输入数据(D)锁存在CK的上升沿上,并将其传输至Q无论输入数据(D)如何,Q均保持不变,直到CK的下一个上升沿换句话说,Q将保留锁存在CK的前一上升沿上的输入数据(D)下面显示了D型触发器的时序图。

有些触发器有一个清除(CLR)或预设(PR)输入引脚,用于将内部状态初始化为已知值 触发器用于异步信号的同步器和数字信号的延迟电路以及计数器、分频器等。

D型触发器的时序图D型触发器的操作 下面通过逻辑示意图说明D型触发器的操作D型触发器由两种D型锁存器组成当时钟的上升沿施加到CK时,D型锁存器#1被激活当时钟(CK)为高电平时,D型锁存器#1保持激活状态,因此D型锁存器#2中的第一个时钟反相器也处于激活状态。

因此,D型锁存器#1中保存的数据将传输到输出(Q),如蓝色箭头所示 即使输入更改状态,输出也将保持不变当时钟下降沿施加到CK时,D型锁存器#2被激活结果,保存在D型锁存器#2中的数据将继续出现在绿色箭头高亮显示的输出端(Q)。

同样,即使输入状态改变,输出也保持不变应该注意的是,直到已知输入在时钟(CK)的上升沿被锁存之前,输出(Q)的值才是未知的。

D型触发器的逻辑符号和真值表

时序逻辑:计数器 计数器示例:74VHC393,74VHC161 计数器在每个时钟(CK)脉冲上按顺序进行递增或递减计数一个4位计数器的模数可达16;一个8位计数器的模数可达256;一个14位计数器的模数可达16384。

某些计数器具有CLR输入,用于将内部状态初始化为已知值计数器集成在数字定时器、电子计算器、秒表和许多其它设备中 计数器大致分为异步(纹波进位)和同步(并行进位)计数器设单个触发器的传输延迟时间为tpd然后,n级异步计数器将产生相当于n×tpd的大延迟。

还应注意,当计数器输出馈送至逻辑门时,异步计数器可能产生风险 74VHC393四位计数器异步:波纹进位计数器

74VHC161四位计数器的逻辑示意图同步:并行进位计数器

时序图:下面显示了一个典型的同步(并行进位)计数器的时序图,它在时钟(CK)的每一个边沿上按顺序进行递增计数。

时序逻辑:移位寄存器 移位寄存器 示例:74VHC164,74VHC165 移位寄存器可以配置为串行-并行(SI-PO)或并行-串行(PI-SO)转换并行-串行转换有助于减少传输线的数量(即传输位宽度)。

某些移位寄存器具有CLR输入,用于将内部状态初始化为已知值下面显示了移位寄存器的逻辑符号和真值表。移位寄存器由多个触发器组成。

移位寄存器的逻辑符号和真值表移位寄存器的操作 下面通过逻辑示意图和时序图说明移位寄存器的操作移位寄存器由级联触发器组成,其中每个触发器的输出端(Q)连接至该链中下一个触发器的数据(D)输入端串行输入(SI)施加至第一触发器的数据(D)输入端。

来自SI的数据在时钟(CK)的上升沿被锁存,并出现在QA处利用四个时钟脉冲,来自SI的数据被传输到第四个触发器结果,串行输入(SI)被转换为并行输出数据出现在QD、QC、QB和QA处

移位寄存器(串行输入,并行输出)的时序图移位寄存器的类型74VHC164八位SI-PO移位寄存器的逻辑示意图

74VHC165八位PI-SO移位寄存器的逻辑示意图

有串行输入/并行输出和并行输入/串行输出移位寄存器。第Ⅳ章:如何读取数据表 读取数据表 本节以74VHC系列IC的数据表为例介绍如何读取数据表。

读取数据表:绝对最大额定值和工作范围 绝对最大额定值(74VHC04FT) 承受超过绝对最大额定值的压力可能会导致IC永久损坏或可靠性下降。

工作范围(74VHC04FT) 此表显示了保证IC功能在正常运行的条件。

读取数据表:直流电气特性 直流电气特性(74VHC04FT)本节介绍如下所示的主要直流特性。

读取数据表:输入电压(VIH和VIL) 直流特性#1:输入电压(VIH和VIL) 确定输入信号为高或低的电压称为阈值电压。 74VHC04FT的直流特性

示例:74VHC04的输入电压(VIH和VIL)与供电电压(VCC) CMOS逻辑IC的VIH和VIL设计为1/2VCC。

读取数据表:输出电流(IOH和IOL)直流特性#2:输出电流(IOH和IOL) 当连接CMOS逻辑IC与LSI芯片时,输出缓冲器的驱动能力和保证的输出电流非常重要。 74VHC04FT的直流特性

示例:74VHC04的输出电流(IOH/IOL)与输出电压(VOH/VOL)曲线CMOS逻辑IC设计用于提供对于IOH和IOL基本相同的驱动能力

读取数据表:输入电流(IIN)直流特性#3:输入电流(IIN) 由于CMOS逻辑IC是电压驱动IC,几乎不需要输入电流(IIN)。 74VHC04FT的直流特性

示例:74VHC04的输入电压(VIN)vs输入电流(IIN)曲线 输入电流(IIN)仅为漏电流,低至几毫微安(nA)。

读取数据表:静态供电电流(ICC) 直流特性#4:静态供电电流(ICC) CMOS器件在非活动状态下消耗的电流比其它类型的器件低得多。 74VHC04的直流特性

示例:74VHC04的静态供电电流(ICC)与供电电压(VCC)曲线 CMOS器件的静态供电电流(ICC)仅为漏电流,低至几毫微安(nA)。

读取数据表:交流电气特性 交流电气特性 74VHC04FT的交流特性

读取数据表:传输延迟时间(tpLH和tpHL)交流特性#5:传输延迟时间(tpLH和tpHL) 理想情况下,输出信号应立即响应输入信号的变化而发生变化,但实际上会存在延迟对应于输入变化而发生输出变化响应所需的时间称为传输延迟时间。

74VHC04FT的交流特性

示例:74VHC04

读取数据表:功耗电容(CPD)交流特性#6:功耗电容(CPD) 随着工作频率的增加,CMOS逻辑IC的电源电流增加。 74VHC04FT的交流特性

示例:74VHC04的输入频率(fIN)与电流(ICC)斜率

读取数据表:输入容限功能 什么是输入容限功能? 具有输入容限功能的CMOS逻辑IC允许在电源激活或在0V时向输入端施加高达最大工作电压的电压输入容限功能允许电平从较高电压转换为较低电压。

电平转换示例从5V向下转换至3V:采用74VHC或74LCX系列。从3V向下转换至到1.2V:采用74VCX系列。

以下是典型CMOS逻辑IC的等效电路在输入侧插入二极管以进行ESD保护,而输出侧的二极管是寄生二极管如果施加的电压高于VCC或在IC断开时施加电压,则输入端和电源之间的二极管可能会导通在这种情况下,产生的大电流可能会损坏IC。

通过使用具有输入容错功能的IC,即输入端和电源之间无二极管的IC,可以防止器件损坏

很容易区分一个IC是否具有输入容错功能让我们看一下TC74HC和74VHC系列IC的数据表 请参阅工作范围表中显示的输入电压TC74HC系列的数据表显示VIN=0至VCC这意味着输入引脚的最大容限为VCC。

因此,TC74HC系列没有输入容错功能相比之下,74VHC系列的数据表显示VIN=0至5.5V,这意味着无论VCC如何,均可将高达5.5 V的电压施加到输入引脚因此,74VHC系列具有输入容错功能。

读取数据表:输出容限功能 什么是输出容限功能? CMOS逻辑IC的输出电路具有图腾柱配置,由如下所示的一对p沟道和n沟道MOSFET组成通常,CMOS逻辑IC在输出端和电源之间有一个寄生二极管。

当在关断状态下向IC施加电压或在打开状态下向具有三态输出的IC(例如74LCX245)施加电压时,寄生二极管就会导通产生的大电流可能会损坏IC即使将高于供电电压(VCC)的电压施加到输出端,电流也不会流入。

具有这种寄生二极管的输出配置的IC中。此IC具有输出容限功能。

很容易区分一个IC是否具有输出容限功能 让我们看一下74VHC和74LCX系列IC的数据表 请参阅工作范围表中显示的总线I/O电压74VHC245的数据表显示VIO=0至VCC这意味着输出引脚的最大容限为VCC。

因此,74VHC245没有输出容限功能相比之下,74LCX245的数据表显示VIN=0至5.5V,这意味着无论VCC如何,总线I/O引脚都可以施加高达5.5V的电压因此,74LCX245具有输出容限功能。

读取数据表:掉电保护 什么是掉电保护? 为降低功耗,具有两个电压范围(VCC1和VCC2)的系统可以提供局部掉电模式,其中由VCC1运行的子系统将被关闭例如,假设在电压范围VCC1内使用74VHC系列74VHC系列在输出端和电源之间具有意外的寄生二极管。

因此,当VCC2>VCC1时,该寄生二极管导通在这种情况下,产生的大电流可能会损坏IC使用既没有输入也没有输出寄生二极管的IC(例如74VHCT、74LCX和74VCX系列)可以防止器件损坏这些系列提供掉电保护。

很容易区分一个IC是否具有掉电保护功能 让我们看一下74VHC和74LCX系列IC的数据表 参见直流特性表 74LCX245的数据手册中指定了断电泄漏电流(IOFF),这表明即使在电源关闭时也几乎没有泄漏电流流动。

因此,74LCX245具有掉电保护功能相反,由于74VHC245在输出端和电源之间有一个寄生二极管,如果在相同条件下进行测试,则会有大电流流过因此,74VHC245没有IOFF调节,也没有掉电保护功能

注:以下四个系列提供掉电保护功能: •74VHCT系列 •74VHCV系列 •74LCX系列 •74VCX系列 对于74VHCT系列,掉电保护由IOPD和IIN指定,而不是由IOFF指定。

以上就是关于《CMOS逻辑IC基础知识_cmos逻辑门电路原理图》的全部内容,本文网址:https://www.7ca.cn/baike/10329.shtml,如对您有帮助可以分享给好友,谢谢。