《学习笔记》--高速电路PCB设计要点_高速pcb设计哪个软件好点

目录:

1.高速pcb设计指南

2.高速pcb设计实战攻略pdf

3.高速pcb设计视频教程

4.高速pcb设计原则

5.高速pcb设计书籍推荐

6.高速pcb教程

7.高速pcb板设计规则

8.高速pcb的定义

9.高速电路pcb设计方法与技巧

10.什么是高速pcb设计

1.高速pcb设计指南

随着器件尺寸的减小,器件引脚信号变化沿的速率变得越来越高,以至于SI(Signal Integrity,信号完整性)问题称为高速电路设计中必须面对的主要问题一般而言,SI与以下几个因素有关:反射、串扰、辐射。

2.高速pcb设计实战攻略pdf

反射是由信号传输路径上的阻抗不连续造成的;串扰与信号的间距有关;辐射则与高速器件自身以及PCB设计均有关1、PCB设计与信号完整性1)信号阻抗匹配信号的阻抗匹配是影响信号完整性最主要的因素对于传输线,必须考虑在信号传输路径上阻抗不匹配而带来的反射,信号的反射可利用反射系数 。

3.高速pcb设计视频教程

ρ\rho 计算:ρ=(Z2−Z1)/(Z2+Z1)\rho=(Z_{2}-Z_{1})/(Z_2+Z_1)式中, Z2Z_2 --反射点之后的线路阻抗; Z1Z_1 --反射点之前的线路阻抗注:始端、传输路径、终端阻抗的不匹配,都会造成信号的反射。

4.高速pcb设计原则

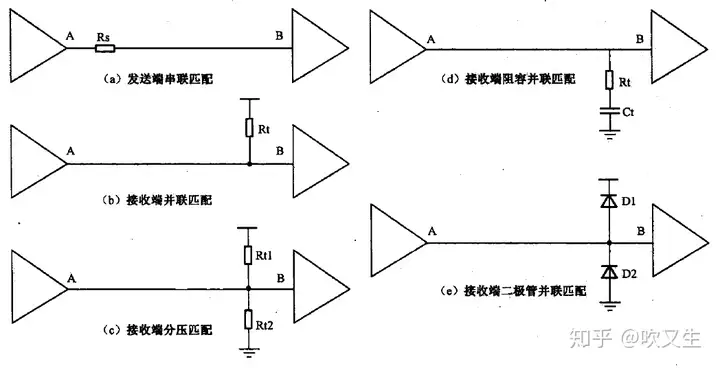

需尽可能减少反射系数 ρ\rho ,即要求 Z2Z_2 尽可能地等于 Z1Z_1 通过在电路上增加元器件以减少 ρ\rho 的方法,称为阻抗匹配设计电路设计中常用的匹配方式有五种:发送端串联匹配、接收端并联匹配、接收端分压匹配、接收端阻容并联匹配、接收端二极管并联匹配,如图1所示。

5.高速pcb设计书籍推荐

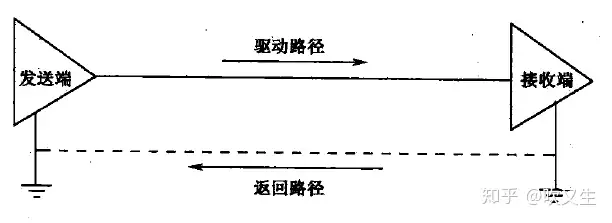

图1 五种阻抗匹配方法2)信号回路信号的传输路径是由两条方向相反的路径构成,一条是驱动路径,由发送端指向接收端,一条是返回路径,由接收端指向发送端。

6.高速pcb教程

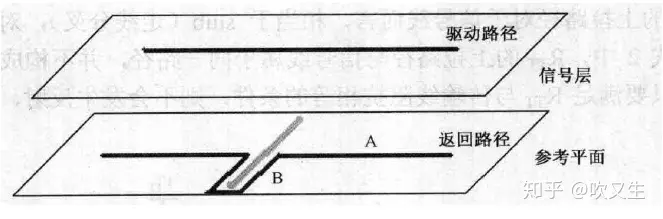

图2 信号回路注:信号传输时,驱动路径即为信号的PCB走线,返回时则选择与驱动路径阻抗最小的路径。返回路径的选择方式如图3所示。

7.高速pcb板设计规则

图3 返回路径的选择信号层的路径将寻找与自身阻抗最小的层作为参考平面,与该信号层距离越近、且平面越完整的层将被选为参考平面在参考平面上,返回路径的选择仍将遵循与驱动路径阻抗最小的原则:在A段,参考平面完整,返回路径完全平行于驱动路径;。

8.高速pcb的定义

在B段,由于存在间隙,从而造成信号路径上阻抗的不连续,将造成信号电平的突变,同时还会引起信号返回路径上的串扰注:信号回路与参考平面的选择密切相关,一般而言,高速信号应选择完整的地平面作为参考平面,如果受层叠结构的限制。

9.高速电路pcb设计方法与技巧

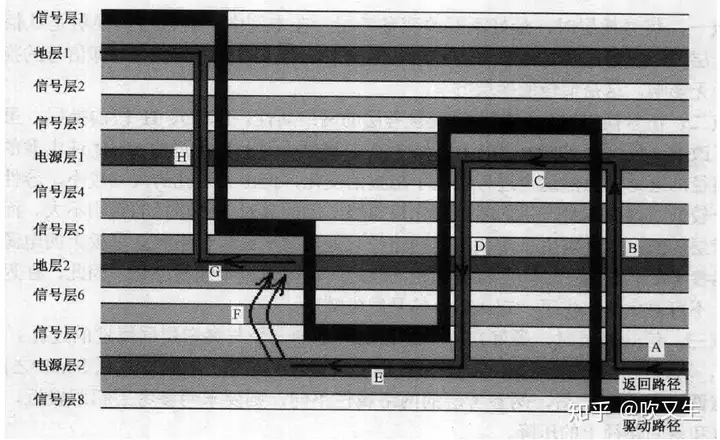

,高速信号所在层距离地层较远,也应该选择完整的电源平面作为参考平面;若受布局和不限的限制,PCB上无法提供完整的地平面或电源平面,那至少应确保与高速信号驱动路径相对应的返回路径上无电气间断信号换层实例,如图4所示。

10.什么是高速pcb设计

图4 信号换层时返回路径示例3)器件内核多感知到的电源或地相对PCB电源或地平面的电平波动称为地弹保持信号回路的低阻抗,同样有利于减少地弹4)串扰串扰是指信号线之间由互感、互容而引起的耦合,由于这总耦合的存在,当某一信号线发生电平的翻转时,在附近的信号线上将感应到一定程度的噪声。

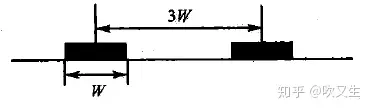

抑制噪声的方法:控制高速信号线之间的间距和平行走线的长度,多个高速信号长距离平行走线时,其间距应遵循3W原则,如图5所示。

图5 3W原则3W原则指两相邻信号线的中心距不少于信号线线宽的3倍,当满足3W原则时,信号之间由互感、互容而产生的互扰可减少70%降低信号的边沿速率5)微带线和带状线微带线指走线在PCB表层,且仅与一个参考层相邻的信号线;。

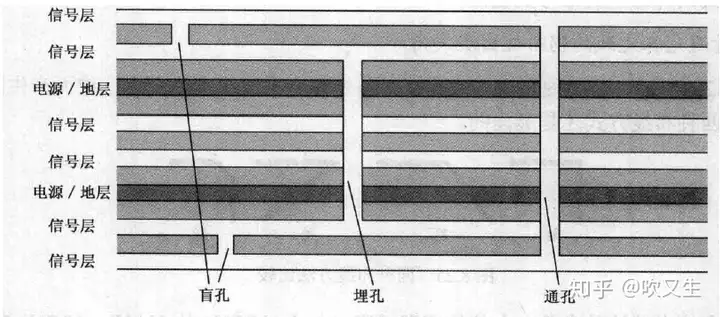

带状线指走线在PCB内层,位于两个参考线之间的信号线。注:在设计中,高速信号的走线应尽量采用带状线而不是微带线。6)盲孔、埋孔技术

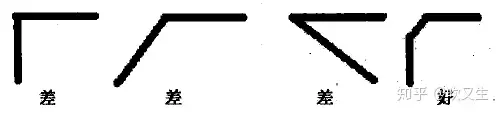

图6 盲孔、埋孔和通孔优点:盲孔、埋孔的出现,使更高密度的单成为可能;盲孔、埋孔有助于提高信号完整性;7)布线布线的方式同样影响着信号完整性。(1)尽量避免在走线的拐角处出现尖角。如图7所示。

图7 四种布线方法比较(2)尽量避免布线过程中线宽的变化(应避免出现线宽不一致的现象)(3)蛇形线,为了时序的要求,经常需要绕线以满足信号的长度,蛇形线是绕线时常用的手段,但应注意:平行线的长度和线段之间的间距,。

对信号完整性和时序都有影响(应满足3W原则;高频关键信号尽量不走蛇形线)(4)谨慎控制高速信号过孔的数目(5)走线分叉--stub为减少stub,需要注意:信号分叉处用电阻间隔;高速信号线上过孔引入的stub;。

8)总结信号完整性的设计需要关注的要点:阻抗匹配、回路的连续性和无阻隔、地弹、串扰等;高速信号采用带状线,在成本允许的情况下,采用盲孔、埋孔技术,有利于获得更好的信号完整性;在布线的过程中,应注意避免出现尖角和线宽的变化,绕蛇形线时同样应注意3W的原则;

不能忽略过孔引入的stub.2、PCB设计与电源完整性在高速设计中,器件低电压、高电流成为一种趋势定义电源平面的目标阻抗:Z0=ΔV/ΔIZ_0=\Delta V/\Delta I式中, ΔV\Delta V。

--纹波电压的波动范围; ΔI\Delta I 动态电流的波动范围电源完整性设计的目的:使单板上各处电源与地平面之间的阻抗低于目标阻抗Z0Z_0 ,如何控制电源与地平面之间的阻抗,是电源完整性设计的关键。

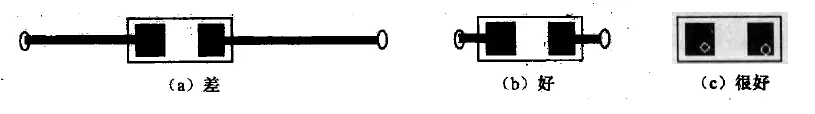

设计要点:1)电源与地层之间的间距,减小电源层与地层之间的间距,有利于减小电源平面的阻抗2)电容的引脚引线电容的作用:①为噪声等干扰提供到地的低阻抗通路;②为电流波动较大的器件提供本地电源“小池塘”在低于谐振频率的频段内,电容表现为容性,反之则表现为感性,而电容的引脚的引线长度在很大程度上决定了谐振频率点的位置。

引线越长,电感性越大,则谐振频率点越低。

图8 去耦电容的引线

图9 增强的去耦电容引脚引线方法3)花焊盘的使用,电源过孔应尽量采用花焊盘过孔,可以提高通流能力,有效散热4)通流能力的计算(主要考虑:电源过孔的通流能力,电源平面的通流能力)Imax=K×T0.44×

A0.725I_{max}=K\times T^{0.44}\times A^{0.725}其中, ImaxI_{max} --最大通流,单位安培(A);KK --降额参数,外层取0.048,内层取0.024;

TT --通流路径上最大容许的温升,单位为 ∘C^{\circ}C ; AA --通流路径的横截面积,单位是平方米尔( mil2mil^{2} )注:一旦出现通流能力不足的情况,可能导致:①电源平面过热,影响电源完整性;②接收端器件的电源输入欠佳。

在应用过程中,还应注意:公式只能用于参考,必须充分降额后才能用对于设计的指导;谨慎地对各项参数的取值,最高容许温升T的取值,分内层和外层;过孔的存在将减少通流路径的横截面积,当路径上存在较多其他信号的过孔时,应相应地增大路径的宽度;

过孔的将外经与内径之间的面积作为通流横截面积3、EMC,电磁兼容性,指在特定电磁环境下,电子设备(或电子元器件)之间相互协调工作的能力包括EMI(电磁干扰)和EMS(电磁敏感度);WMI,指电子设备(或电子元器件)在工作时,产生的不利于其他设备的电磁能量。

EMI包括传导干扰(CE),辐射干扰(RE),谐波干扰等;EMS,指电子设备在工作时,应能承受的外部其他设备的电磁干扰能量,包括传导敏感度(CS)、辐射敏感度(RS)、静电放电(ESD)、浪涌(Surge),电压跌落测试(DIP)等。

EMC设计,应着重在三个方面入手:隔离干扰源、切断干扰传输路径、保护受扰体。

以上就是关于《《学习笔记》--高速电路PCB设计要点_高速pcb设计哪个软件好点》的全部内容,本文网址:https://www.7ca.cn/baike/11505.shtml,如对您有帮助可以分享给好友,谢谢。