芯片后端设计中ESD 原理以及防护介绍(芯片esd保护设计)

在芯片生产过程中,芯片不可避免的要受到各种各样的ESD攻击,包括环境,CMOS工艺,封装,测试以及人体接触都会产生各种各样的静电其中以下两种模型为当前最常见ESD模型:CDM:Charge device model。

HBM:Human body model这两种模型的主要区别是CDM是来自芯片被充电后从内部产生的放电,HBM是来自芯片外部比如PAD对芯片内部的放电总的来讲,HBM的情况并没有CDM的情况复杂:大多数的ESD保护是针对HBM模型的,也就是从I/O pad到VSS/VDD 的保护。

随着工艺的演进,mos期间的栅氧化层越来越薄,所以对CDM的保护也变得越来越重要

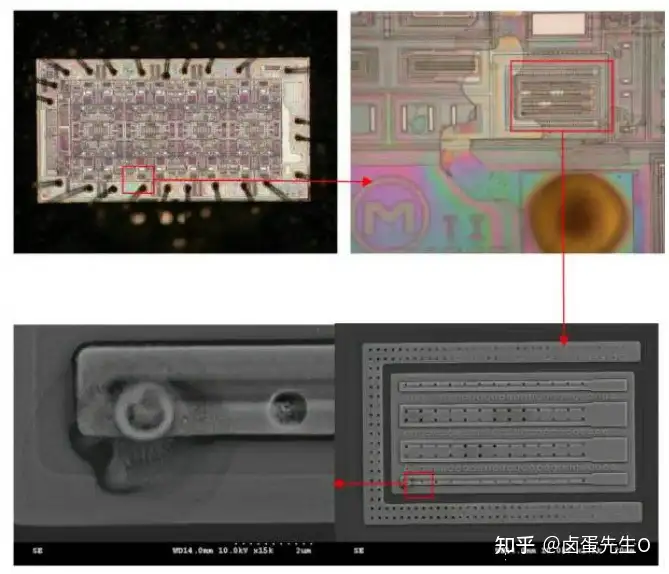

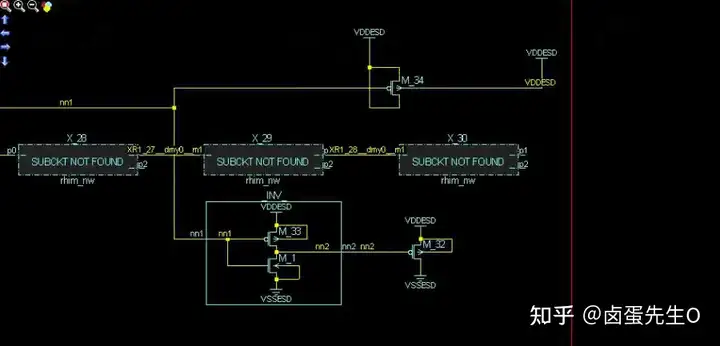

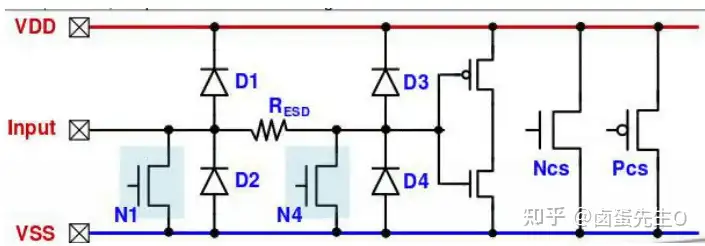

图1 ESD对芯片的损坏下图是根据clamp的网表生成的一个clamp 的电路。

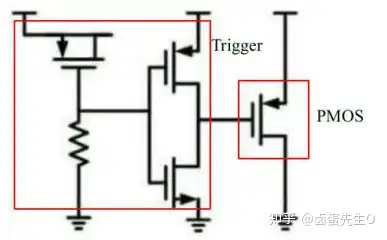

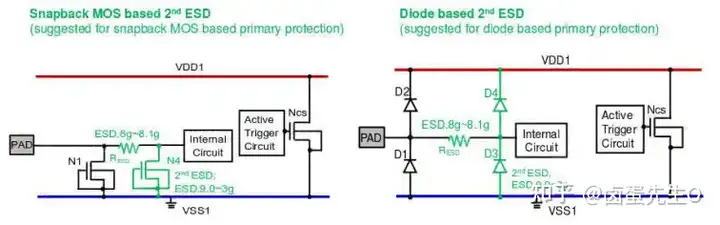

Clamp 电路梳理一下这个电路,如下图,PMOS作为ESD的电流泄放管。当电源处的电压被抬高后,Trigger 电路会打开PMOS管,VDD的大电流会通过PMOS管泄放掉。

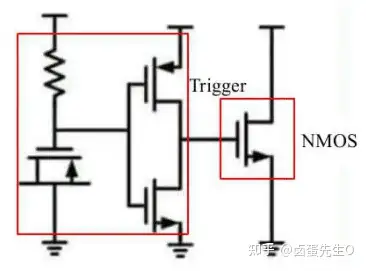

NMOS 也可以作为ESD泄放管,触发的RC电路需要翻过来。NMOS作为ESD的电流泄放管:

N/PMOS 管均可作为ESD泄放管的电路结构。

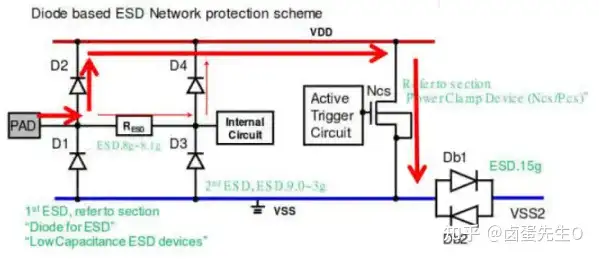

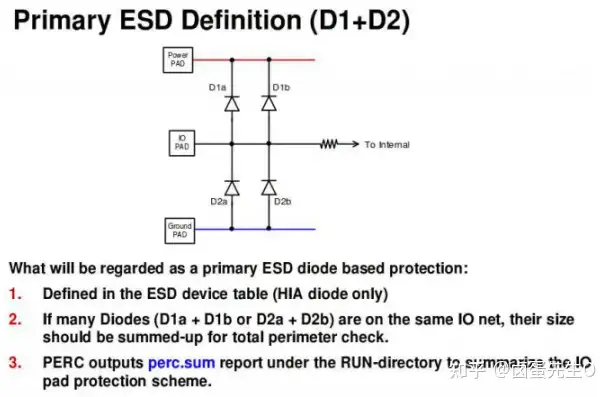

结合下图带IO PAD的电路分析,这个电路是以两级diode 形成钳位电路,将PAD的电位钳位在VSS-0.7V——VDD+0.7V,一旦PAD的电位离开这个范围,钳位电路启动,diode的PN节正偏,直到PAD的电位回落到VSS-0.7V——VDD+0.7V。

如果I/O PAD 进来的ESD大电流没有通过上述路径泄放掉,或者有一部分较大的ESD电流进入了到Internal Circuit电路,极有可能对内部电路造成永久性破坏;导致芯片永久失效。

下图中这个电路也是常见的IO电路一种。

用MOS管形成的diode也可以作为I/O Pad的输入。

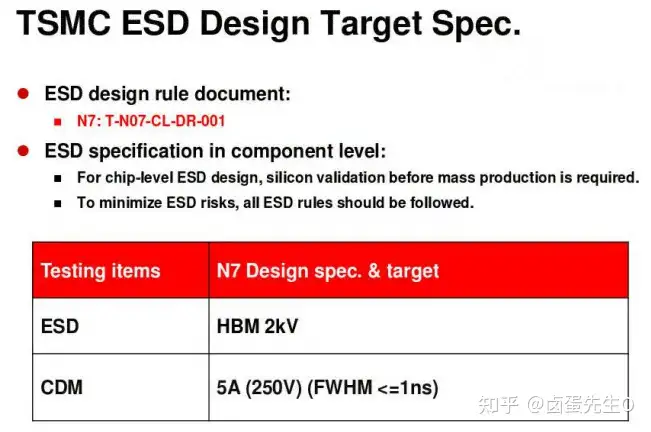

为了最大限度的避免ESD导致的芯片失效风险,TSMC对HBM和CDM这两种模型分别有推荐的ESD耐压值。

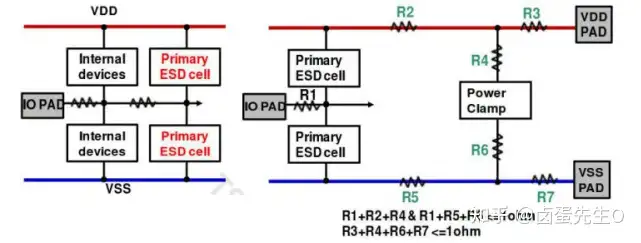

根据欧姆定律,V=IR,电流总会选择阻抗小的路径传输,所以根据芯片的电源规划合适的ESD网络,这些网络中关键路径上电阻大小决定了所规划的ESD保护是否能够在ESD大电流来临的时候保护好芯片的内部电路所以,ESD里面大量的rule 是来检查电流泄放通路是否满足一定的阻抗要求,如果不满足,就极大的可能导致ESD保护失效。

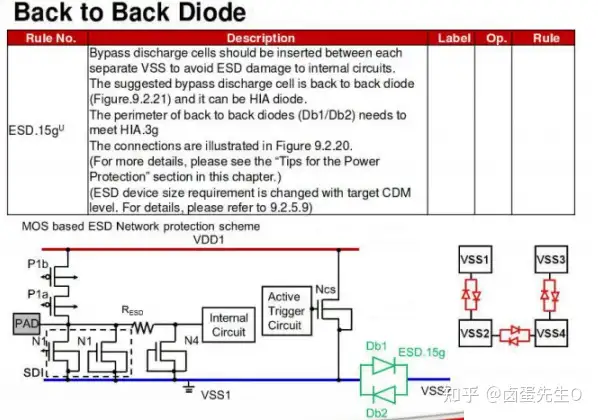

B2BDiode 作用:

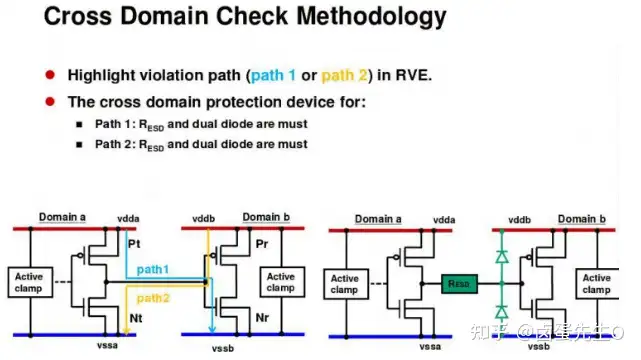

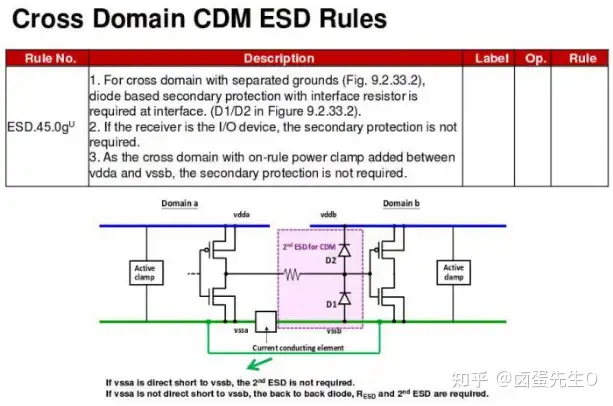

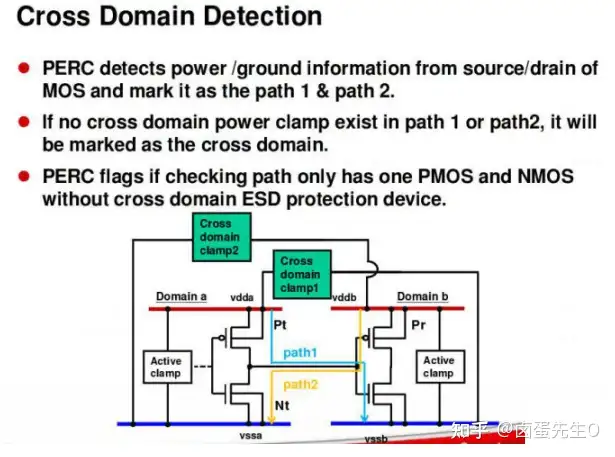

Cross Domain 下接口处的ESD检查路径:

Cross domain 的ESD检查。(注意:vssa和vssb属于同一个地活着分开地,对CDM cell 的要求是不一样的)。

Cross domain 典型的ESD网络布局(只添加了cross domain clamp ,没有添加CDM cell)。

小编码字不易,觉得有收获的话各位看官给个赞呗~下面是我自己的个人公众号:丹青芯履,主要分享芯片后端设计中常见问题,希望大家多多关注谢谢!

以上就是关于《芯片后端设计中ESD 原理以及防护介绍(芯片esd保护设计)》的全部内容,本文网址:https://www.7ca.cn/baike/3353.shtml,如对您有帮助可以分享给好友,谢谢。