时序电路·专题04·计数器_时序器工作原理

目录:

1.时序计数器的最大优点和最大缺点各是什么?

2.时序计数器是什么

3.计数器时序图

4.时序电路(计数器,移位寄存器)

5.计数器时序图怎么看

6.时序逻辑电路计数器的定义和作用是什么?

7.计数器及时序电路设计

8.计时器时序图

9.时序逻辑电路计数器

10.时序器的用法

1.时序计数器的最大优点和最大缺点各是什么?

引言计数器是最常用的时序电路之一,它们不仅可用于对脉冲进行计数,还可用于分频、定时、产生节拍脉冲以及其他时序信号按触发器动作分类按编码数值增减分类按编码分类(1)【同步】计数器(1)【递增】计数器(1)【二进制码】计数器。

2.时序计数器是什么

(2)【异步】计数器(2)【递减】计数器(2)【BCD码】计数器……(3)【可逆】计数器(3)【循环码】计数器计数器运行时,从某一状态开始依次遍历【不重复】的各个状态后完成一次循环,所经过的【状态总数】

3.计数器时序图

称为计数器的【模 】()(Modulo)(Modulo) ,并用 MM 表示若某个计数器在 nn 个状态下循环计数,通常则称之为模nn计数器,或 M=nM=n 计数器例如一个在60个不同状态中循环转换的计数器,就可称为模60,或 。

4.时序电路(计数器,移位寄存器)

M=60M=60 计数器有时也把模 nn 计数器称为 nn进制计数器一、N位二进制计数器按照【二进制数】自然【递增】或【递减】编码的计数器称为二进制计数器()(BinaryCounter)(Binary Counter)。

5.计数器时序图怎么看

, NN 位二进制计数器的模为 2N2^{N} ,由 NN 个触发器组成1-1:N位【异步】二进制计数器图6.5.7是一个4 位异步二进制计数器的逻辑图,它由4个下降沿触发的 T′T 触发器组成

6.时序逻辑电路计数器的定义和作用是什么?

计数脉冲 CP¯\bar{CP} 加至触发器 FF0FF_{0}的时钟脉冲输入端,每输入一个计数脉冲, FF0FF_{0} 翻转一次 FF1FF_{1} 、 FF2FF_{2} 和 FF3FF_{3} 都以前级触发器的

7.计数器及时序电路设计

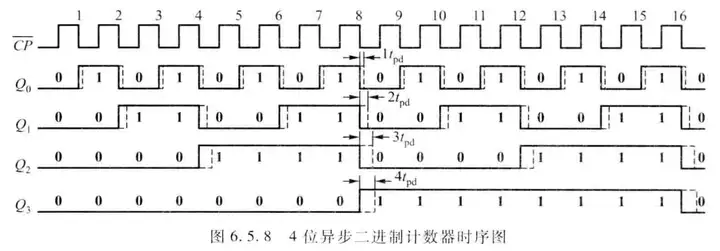

QQ 端输出作为触发信号,当 Q0Q_{0} 由1变0时, FF1FF_{1} 翻转,其余类推。分析其工作过程,不难得到输出波形如图6.5.8所示。

8.计时器时序图

由图可见,从初态0000(可由 CR¯\bar{CR} 输入低电平脉冲使4个触发器全部置0)开始,每输入一个计数脉冲,计数器的状态就按二进制编码值递增1,输入第16个计数脉冲后,计数器又回到0000状态。

9.时序逻辑电路计数器

显然,该计数器以16 个 CPCP 脉冲构成一个计数周期,是模16 ()(M=16)(M=16) 递增计数器其中, Q0Q_{0} 的频率是 CP¯\bar{CP} 的1/2,即实现了【2分频】, Q1

10.时序器的用法

Q_{1} 得到 CP¯\bar{CP} 的【4分频】以此类推,Q2Q_{2}、Q3Q_{3}分别对 CP¯\bar{CP} 进行了【8分频】和 【16 分频】,因而,【计数器】也可作为【分频器】使用异步二进制计数器的工作原理和结构均较简单,但各触发器不是在同一时钟沿作用下同时翻转,而是

逐级脉动翻转实现计数进位的,故亦称之为【纹波】计数器()(RippleCounter)(Ripple Counter) 图6.5.8中的虚线是考虑了触发器逐级翻转过程中平均传输延迟时间tpdt_{pd}。

的波形由于各触发器不在同一时间翻转,因此,若用这种计数器驱动组合逻辑电路,则可能出现【瞬间错误】的逻辑输出例如,当计数值从0111加1时、 Q3Q2Q1Q0Q_{3}Q_{2}Q_{1}Q_{0} 要先后经过0110、0100、0000 几个状态,才最终翻转为1000。

另外,当计数脉冲频率很高时, Q3∼Q0Q_{3}\sim Q_{0} 甚至会出现编码输出分辨不清的情况对于一个 NN 位二进制异步计数器来说,从一个计数脉冲作用在第一个触发器开始,到第 NN 个触发器翻转达到稳定状态为止,需要经历的时间为 。

N·tpdN·t_{pd} 为了保证正确地检出计数器的输出状态,必须满足 >N·t_{pd}">TCP>>N·tpdT_{CP}>>N·t_{pd} 的条件,其中, TCPT_{CP} 为计数脉冲 CP

¯\bar{CP} 的周期1-2:N位【同步】二进制计数器为了提高计数速度,可采用同步计数器其特点是,计数脉冲作为时钟信号同时接于所有触发器的时钟脉冲输入端在每次计数脉冲沿到来之前,根据当前计数器状态,利用【。

组合逻辑】电路产生触发器的【激励】条件当计数脉冲沿到来时,所有应翻转的触发器同步翻转同时,所有应保持原状态的触发器不发生变化由于不存在异步计数器那种纹波进位造成的延迟时间积累,所以能取得较高的计数速度,输出编码也不会发生纹波进位时的那种混乱。

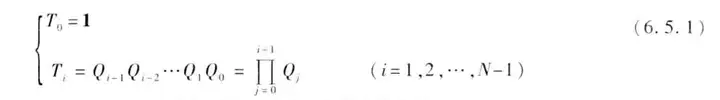

显然,同步计数器是一种同步时序电路。——1)工作原理表6.5.5是4位二进制计数器的转换表。

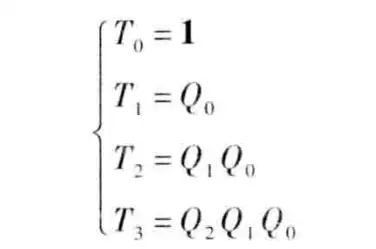

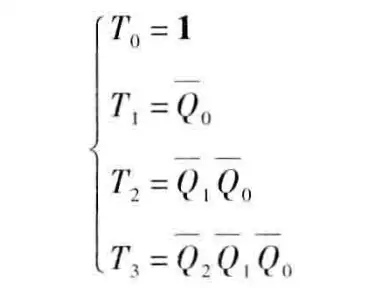

观察该表【递增计数】一栏可以看出,Q0Q_{0} 在每个计数脉冲作用后都要翻转一次;Q1Q_{1}只在Q0=1Q_{0}=1的条件下接受计数脉冲作用而翻转;Q2Q_{2}则在Q0=Q1=1Q_{0}=Q_{1}=1

的次态翻转;Q3Q_{3}在Q0=Q1=Q2=1Q_{0}=Q_{1}=Q_{2}=1的次态翻转当用 TT 触发器实现4 位同步二进制递增计数器时,可根据上述激励条件,确定每个 TT 触发器的激励方程为。

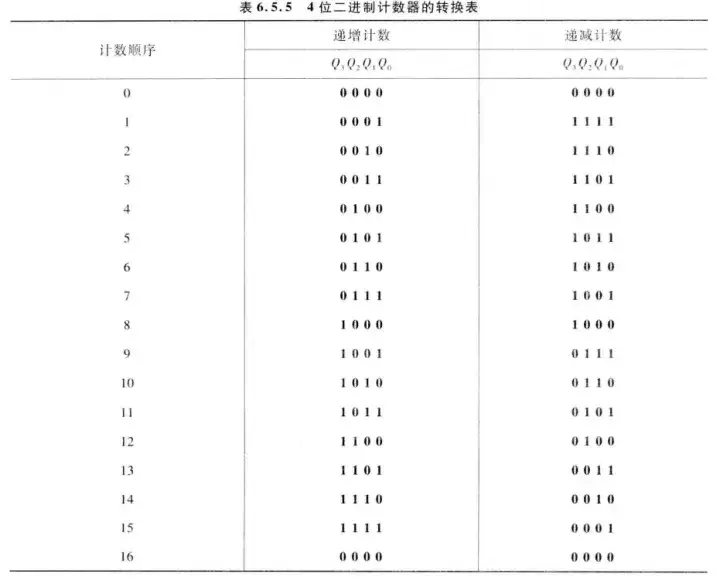

即除了触发器 FF0FF_{0} 的 T0=1T_{0}=1 外,其他触发器都是在比其低的各位均为1时准备好翻转条件由此类推,可以扩展到更多的位数当用 NN 个 TT 触发器构成 NN 位同步二进制【递增】计数器

时,各触发器的【激励】方程为

由表6.5.5【递减计数】一栏可以看出

Q0Q_{0} 同样在每个计数脉冲沿到来时都要翻转一次;而其他位都是在比其低的各位均为0时准备好翻转条件,在次态完成翻转,实现二进制计数的递减借位当用 TT 触发器实现4 位同步二进制【递减】计数器时,

激励方程为

对于 NN 位同步二进制递减计数器,类似地有

根据式(6.5.1)和式(6.5.2)可得由 TT 触发器构成的4位同步二进制计数器逻辑图如图6.5.9所示。其中,图(a)为递增计数器

图(b)为递减计数器

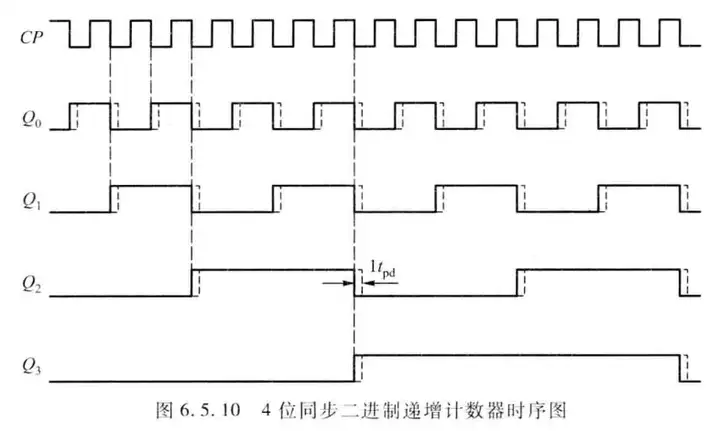

图6.5.10所示是图6.5.9(a)所示计数器的时序图,其中虚线是考虑到触发器传输延迟时间 tpdt_{pd} 的波形。

递增计数器的图由图6.5.10可知,在同步计数器中,由于计数脉冲CPCP同时作用于各触发器,所有触发器的状态更新几乎是同时进行的,都比计数脉冲沿的作用时间滞后一个tpdt_{pd} 因此,输出状态比异步二进制计数器稳定。

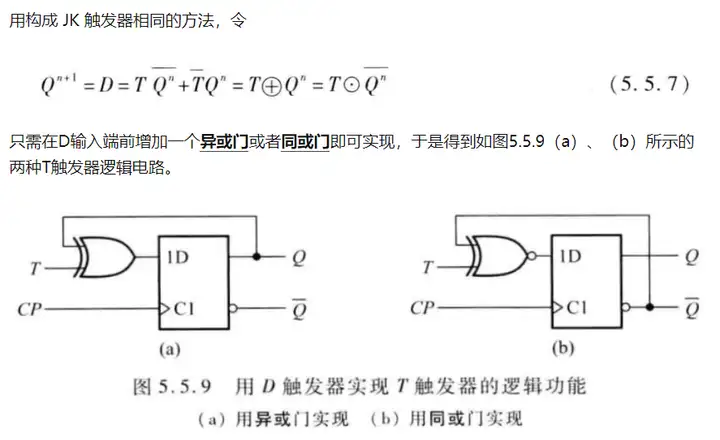

对于同一逻辑系列,位数相同的计数器,同步计数器的工作速度一般高于异步计数器。DD 触发器与 TT 触发器的关系如下:

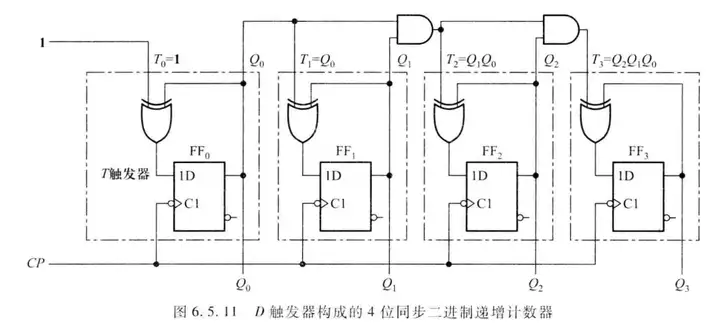

故当用 DD 触发器实现二进制计数器时,可根据图5.5.9(a) DD 触发器与 TT 触发器的关系,得到 DD 触发器构成的4 位二进制递增计数器如图6.5.11 所示。

其中,4 个点画线方框内为等效的 TT 触发器——2)同步【串行】计数器递增计数器的低位计满后激励高位触发器翻转的操作称为计数进位图6.5.11所示电路的进位信号是通过一系列串行的逻辑门逐位向高位传递的,这种计数器称为。

同步【串行】计数器如果一个计数器中有 NN 位触发器,将它们按二进制数位从低位向高位编号,最低位输出为 Q0Q_{0} 那么,Q0Q_{0}的进位信号至少要经过 N−2N-2 个等效逻辑门的延迟,才可能到达最高位触发器的输入端。

假设每个等效逻辑门的延迟时间相同,均为 tGpdt_{Gpd},那么计数器中组合电路的最大延迟时间为

显然, ()tCOMpd(max)t_{COMpd(max)} 将随着计数器的位数增多而增大当计数器位数较多时,会降低电路的运行质量,或被迫降低电路的工作频率——3)同步【并行】计数器另一种计数器是同步【并行】计数器

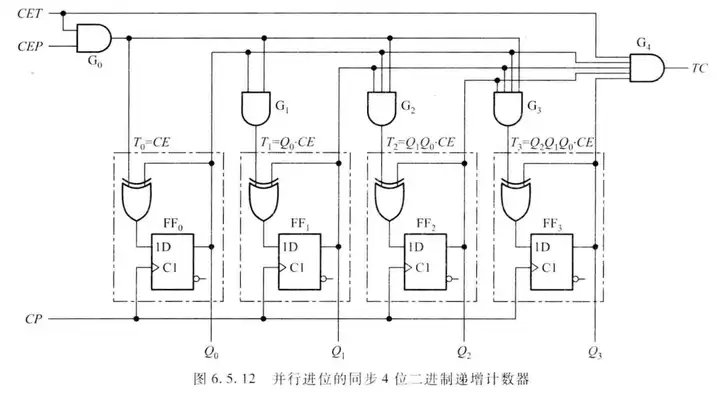

,电路结构如图6.5.12所示,其激励电路由 、、G1、G2、G3G_{1}、G_{2}、G_{3} 三个与门实现。

和图6.5.11所示电路相比,虽然图6.5.12中各触发器的激励方程与前者相同,但后者在一次状态转换完成后,只需经过相当于一个等效逻辑门的传输延迟时间 tGpdt_{Gpd} 就可将激励信号传递到所有高位触发器的

TT 输入端,迎接下一个 CPCP 触发沿的到来即无论计数器有多少位,电路的 ()tCOMpd(max)t_{COMpd(max)} 都等于一个等效逻辑门的传输延迟时间 tGpdt_{Gpd} 因此,这种进位方式可以大大提高计数器的工作频率,位数越多,提高越明显。

然而,随着计数器位数的增多,【低位】触发器的【扇出】和【高位】触发器激励电路的【扇入】会【增多】例如,从图6.5.12 所示电路中 Q0Q_{0} 的扇出和 G3G_{3}门的扇入就可看出这一点当计数器规模达到4 位以上时,工程上常常采用折中处理的方案,将并行进位和串行进位相结合。

。方法是将多位计数器分为若干组,组内的触发器采用并行进位,而组与组之间的进位则以串行实现。图6.5.13示出按这种方案实现 16 位同步二进制计数的一个实例。

图中使用了4 组图6.5.12所示电路,各组从低位到高位分别以 C0∼C3C_{0}\sim C_{3} 命名需要注意的是每一组中串行进位允许信号 CETCET 、并行进位允许信号 CEPCEP 和进位输出信号

TCTC 的连接方法。其中

是向高位组的进位信号对于 C0C_{0} 组, CETCET 与 CEP CEP相连,可作为整个计数器的使能输入 CECE ,当 CE=1CE=1 时允许计数其他各组的 CEPCEP 均接收C0C_{0}

组计数器的进位信号TC0TC_{0};C1C_{1}组 CETCET 直接与计数允许输入相连,、C2、C3C_{2}、C_{3}组的 CETCET 接收相邻低位组的进位信号电路工作时,只有在 C0C_{0}。

组发出进位信号,即 TC0=1TC_{0}=1 后,才允许所有高位组内部进行并行进位操作;高位各组的进位信息则通过各自的 G4G_{4} 直接上传很容易看出, C0C_{0} 组 Q0Q_{0} 的翻转信号,只需经过该组的 。

G4G_{4} 和 C3C_{3} 组的 、G0、G3G_{0}、G_{3} 三个等效逻辑门的延迟,历时大约 3tGpd3t_{Gpd} ,就能抵达整个计数器的最高位触发器,也就是 C3C_{3} 组的

FF3FF_{3} 进一步分析可以证明,电路中所有触发器的激励电路延迟都不会大于3tGpd3t_{Gpd},即 ()tCOMpd(max)≈3tGpdt_{COMpd(max)}\approx 3t_{Gpd}。

因而,这种并、串行结合的进位方法既具有较短的进位延迟,又同时兼顾了电路的复杂程度图6.5.13所示的进位方法,对于设计大型同步计数器是具有普遍意义的,包括 PLD和 ASIC 的应用例如,在高速数据采集系统中,经常需要用计数器对。

1K 以上"字节 (8 bit) "或"字 (16bit) "的存储器实现与取样同步的高速地址扫描,以便及时将采集的数据顺序存入存储器用于这种目的的二进制计数器,位数一般都超过10位,如果采用并、串行结合的进位方式,则可提高电路工作的可靠性,或充分发挥已有电路的资源。

——3)异步清零和同步并行置数图6.5.14 所示电路是功能更为完备的4 位同步二进制计数器的逻辑图。

在许多应用中,需要计数器从零状态开始工作,为此,在图6.5.14 所示电路中增加了直接清零输入端 \bar{CR} 可以看到,清零信号\bar{CR}直接作用于4 个触发器的置0端当异步的\bar{CR}。

为低电平时,将使电路中所有触发器无条件置0,而不管其他输入端是何状态(包括时钟信号 CP ),因此,\bar{CR}=0对计数器状态有优先级最高的控制权,其他各种操作都是在\bar{CR}=1的条件下才能执行。

计数器应用时,有时需要将计数器预置为某种状态,然后再从该状态开始计数图6.5.14所示电路以图6.5.12为基础,在每个 D 触发器的输入端前插入一个2 选1数据选择器,以选择从数据输入端 D_{N} 置入数据,还是执行正常的计数功能,并用一个公共置数控制端

\bar{PE}进行控制由图6.5.14 看出, D_{3}D_{2}D_{1}D_{0} 为4位并行数据输入端,当 \bar{PE}=0 时,数据选择器选择并行数据送至相应触发器的 D 输入端,这样,在下一个 。

CP 沿到来时,输入端D_{3}D_{2}D_{1}D_{0}的数据被并行置入各触发器这种在时钟脉冲作用下的并行置数称为【同步】置数而当 \bar{PE} 恢复高电平后,4个2选1数据选择器选择相应异或门

的输出信号送至触发器 D 输入端,计数器恢复正常计数功能,于是,可在预置数据的基础上继续递增计数由图6.5.14看出,\bar{PE}=0具有次高优先级,仅低于\bar{CR}=0,计数和保持状态的操作都要求。

\bar{PE}=1——4)典型集成同步二进制计数器74LVC161 是一种典型的高性能、低功耗CMOS 4位 同步二进制递增计数器芯片的逻辑功能和实现原理与图6.5.14所示逻辑图相同它的时钟最高工作频率可达 。

200MHz 。图6.5.15所示为 74LVCI61 的引脚功能图,所有引脚名称与图6.5.14 所示输入/输出信号线一致。

表6.5.6示出它的功能表。

74LVC161 的典型时序图如图6.5.16所示。

图中,当清零信号 \bar{CR}=0 时,各触发器置0当\bar{CR}=1时,若\bar{PE}=0,在下一个时钟脉冲上升沿到来后,各触发器的输出状态与预置的输入数据相同在\bar{CR}=\bar{PE}=1。

的条件下,若 CEP=CET=1 ,则电路处于计数状态图中从预置的1100开始计数,直到 CEP·CET=0,计数状态结束此后处于禁止计数的保持状态∶Q_{3}Q_{2}Q_{1}Q_{0}=0010进位信号TC只有在 。

Q_{3}Q_{2}Q_{1}Q_{0}=1111 且 CET=1 时输出为1,其余时间均为0与 74LVC161 工作原理和功能相似的集成计数器还有 74LVC163 ,其差别仅在于清零方式不同,后者为。

同步清零,即清零信号 \bar{CR} 的低电平必须等待下一个 CP沿作用后才能完成清零操作另外,与它们结构类似的计数器还有 74LVC160 和 74LVC162 ,这两种计数器是 8421BCD。

计数器,前者为异步清零,后者为同步清零二、其他模数的计数器除了模为 2^{N} 的二进制计数器外,工程上还经常需要很多其他模数的计数器这类计数器的状态中都或多或少存在无效状态,它们也分为同步和异步,递增、递减和可逆

等各种类型。其中,最常用的是 BCD计数器。2-1:异步 BCD计数器在例6.4.2中曾分析过一个具有000~100 五个连续二进制编码状态的异步计数器。

例6.4.2如果在该电路基础上增加一级触发器,便可构成异步 BCD 计数器,如图6.5.17所示。

为了应用的灵活性,除清零信号 CR 外,这个触发器和五状态计数器的输入、输出端均是独立引出的。——1)模10计数器

2-2:用集成计数器构成任意模数计数器 任意模数的计数器可以用厂家定型的集成计数器产品外加适当的电路连接而成用模 m 的集成计数器构成模 n 计数器时,如果 n">m>n ,则只需一个模 m 集成计数器;如果 。

m

————2)反馈清零法的应用

————3)反馈置数法的概念

————4)反馈置数法的应用1

————5)反馈置数法的应用2

——2)模24计数器(双芯片)

2-3:环形计数器 ——1)基本环形计数器

如果将图6.5.2中移位寄存器的 D_{SO}(Q_{3}) 与 D_{SI} 相连,则构成环形计数器,如图6.5.22(a)所示。

若事先通过 \bar{PE} 端施加低电平脉冲,在4个触发器内置入数据 Q_{3}Q_{2}Q_{1}Q_{0}=0001 ,那么环形计数器在 CP 脉冲用下,将会有如图6.5.22(b)所示的4个状态。

于是,电路成为模4计数器。图 6.5.22(c)所示为在4个 CP 脉冲作用下的波形。

可以看出,这种计数器不必译码就能直接输出 4 个状态的译码信号,亦不存在普通译码电路输出易出现的竞争-冒险现象——2)扭环形计数器 上述基本环形计数器的状态利用率不高,4 个触发器只有4 个计数状态

若将图6.5.2所示电路中的 \bar{Q_{3}} 与 D_{SI} 相连,则构成扭环形计数器,亦称为约翰逊计数器(Johnson counter),电路的状态将增加一倍。

图6.5.23(a)所示是5个触发器构成的扭环形模10计数器,图6.5.23(b)所示是其状态图,表6.5.8列出了它的十个状态以及对各状态译码的逻辑表达式。

可以看出,它的译码电路将十分简单由于每一次时钟脉冲触发沿到来后只有一个触发器改变状态,所以译码输出不会出现竞争-冒险图6.5.23(a)中附加的逻辑门使电路能够自校正,请读者自行验证74HC4017是一种典型的模10扭环形计数器,芯片中含有计数器的十个有效状态的译码电路,从引脚可直接得到 。

D_{0}\sim D_{9} 无竞争-冒险的译码输出。 ————

以上就是关于《时序电路·专题04·计数器_时序器工作原理》的全部内容,本文网址:https://www.7ca.cn/baike/7930.shtml,如对您有帮助可以分享给好友,谢谢。