基本结构与工作原理

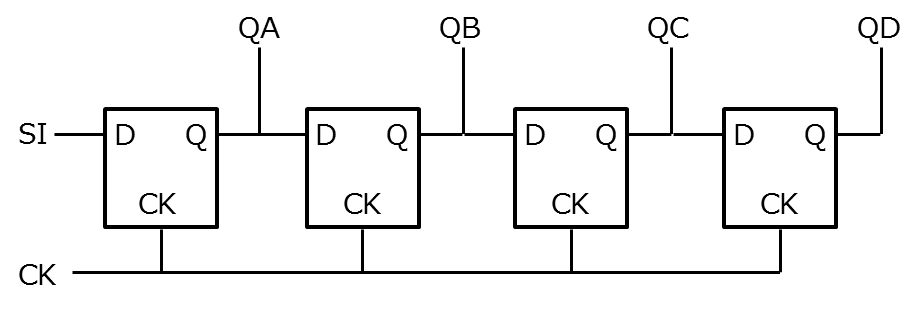

移位寄存器由多个触发器级联构成,每个触发器的输出端连接至下一级的输入端。时钟信号同步控制数据传递节奏,当有效边沿触发时,存储的二进制信息按指定方向移动一位。数据输入模式分为串行和并行两类,串行模式下信息逐位进入首级触发器,并行模式则通过多路端口同时加载数据。典型器件包含移位控制端,通过电平切换决定数据保持或流动状态。

方向控制机制

双向移位寄存器配备方向选择引脚,高电平时执行右移操作,低电平触发左移功能。某些型号集成循环模式,末端触发器的输出回馈至首级输入端,形成闭环结构。机械旋转编码器常配合此类设计,将物理转动量转化为数字脉冲序列。工业控制系统利用方向可控特性实现双向计数,在位置检测装置中具有关键作用。

时序参数特性

建立时间和保持时间是评估性能的核心指标,分别指数据在时钟边沿前后的稳定窗口。74HC164型移位寄存器典型建立时间为12ns,保持时间要求不低于5ns。时钟偏移容忍度决定器件在非理想信号下的可靠性,高速型号通常集成锁相环电路补偿时序误差。温度系数影响延迟稳定性,军工级器件在-55℃至125℃范围内保证时序参数不超差。

集成电路实现方案

CMOS工艺制造的4000系列器件具有微功耗特性,静态电流小于1μA,适合电池供电场景。TTL兼容的74LS型号驱动能力达8mA,可直接驱动LED阵列。级联扩展时需注意负载匹配,超过四级级联建议加入总线驱动芯片。某些FPGA内置可配置移位单元,支持动态位宽调整,在协议转换器中展现灵活优势。

噪声抑制技术

电源引脚配置0.1μF陶瓷电容可有效滤除高频干扰,布局时尽量缩短去耦元件引线。施密特触发器输入结构能抑制30%Vcc以下的电压波动,提升工业环境适应性。双绞线传输时钟信号配合差分接收电路,可将共模噪声抑制比提高至60dB。金属屏蔽罩应用在射频敏感场合,能降低15dB以上的电磁辐射干扰。

故障诊断方法

采用特征分析法定位故障单元,向寄存器注入全1模式后观察输出序列完整性。热像仪可发现过流损坏的芯片区域,异常温升点往往对应内部短路单元。边界扫描技术通过JTAG接口访问内部节点状态,无需物理探针即可完成在线测试。数据滞留现象多由时钟信号畸变引起,需用示波器检测上升沿是否满足最小斜率要求。

特殊功能变体

桶形移位器支持任意位数的循环位移,在加密算法处理中执行比特置换操作。带预置位的型号允许异步加载初始值,用于产生特定模式的同步信号。三态输出型可实现总线共享,多个器件分时接入同一数据通道。某些音频处理芯片集成串并转换移位器,将I2S流数据转换为DAC所需的并行格式。

信号完整性维护

传输线效应在时钟频率超过50MHz时显著显现,终端匹配电阻可消除23%以上的信号反射。过冲电压限制在供电电压的20%以内,防止栅氧层击穿损坏。相邻信号线间距保持两倍线宽以上,降低30%的串扰概率。电源完整性分析显示,独立电源平面可使地弹噪声降低40mV,对16位以上移位链尤为重要。

功耗优化策略

门控时钟技术可使动态功耗下降65%,通过使能信号控制时钟树通断。多阈值晶体管布局将静态漏电流抑制在100nA量级。数据保持型寄存器在休眠模式下关闭移位功能,仅维持存储单元供电。分段供电设计对高位寄存器特别有效,非工作区段可完全断电,整体能效提升22%。

应用场景实例

在矩阵键盘扫描电路中,移位寄存器产生逐行激活信号,同时读取列线状态。液晶模块驱动时,将像素数据串行移入,利用锁存脉冲同步更新显示内容。数字温度传感器通过单线接口发送移位寄存器格式的数据帧,包含12位量化结果和CRC校验码。电机驱动系统采用移位寄存器生成相序控制波形,精确管理步进角度和旋转方向。

免责声明:文章内容来自互联网,版权归原作者所有,本站仅提供信息存储空间服务,真实性请自行鉴别,本站不承担任何责任,如有侵权等情况,请与本站联系删除。

转载请注明出处:移位寄存器的功能实现与技术特性(移位寄存器) https://www.7ca.cn/zsbk/zt/53755.html