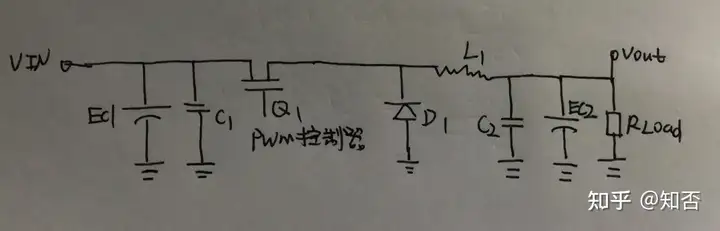

BUCK电路设计详解与设计调试-1(buck电路原理图)

工作原理

图一当Q1导通时,Vin通过Q1给电感与负载电容充电以及负载供电,假设忽略Q1上面导通压降,L1两端的电压为:ΔV=Vout−Vin=LΔiTon\Delta V=Vout-Vin=L\frac{\Delta i}{Ton}

---------- 1当Q1截止时,电感L1与负载电容对负载进行放电,其中二极管D1起到续流的作用,假设忽略二极管D1两端的电压降,L1两端的电压为:

ΔV=Vout−0=L−ΔiToff\Delta V=Vout-0=L\frac{-\Delta i}{Toff} ---------- 2

其中Ton为开关Q1的导通时间,Toff为开关Q1的截止时间, Δi\Delta i 为电感L上面的电流变化量,无论从公式1或者2都可以看出来,在导通时间,周期,电感,以及输入输出电压固定的情况下,电感上面的电流都是线性变化的,在Ton时刻电感充电,电流增大,故为正值;在Toff时刻,电感放电,电流减小,故为负值。

由公式1与公式2合并同类项可以得出:占空比VoutVin=TonTon+Toff=TonT=占空比\frac{Vout}{Vin}=\frac{Ton}{Ton+Toff}=\frac{Ton}{T}=占空比

----------3由3式可以得出结论: 1,理想状态下,输入输出电压的关系只与电路的占空比有关 这里也可以延展出buck电路的控制原理,当buck电路的输出,或者输入变化时,系统检测到差异,会通过调节PWM波形的占空比来维持系统的稳定。

由于负载效应,当输出电压被负载拉低的时候,PWM控制器会使Ton的时间增大使Vout维持稳定;同理,在由于负载变轻,电压变高后,可以通过减少导通时间来使Vout降低,维持系统稳定Vout变高了会通过降低占空比来降低电压,Vout变低了会通过增大占空比来增大电压,所以我们就看到了稳定的电源系统。

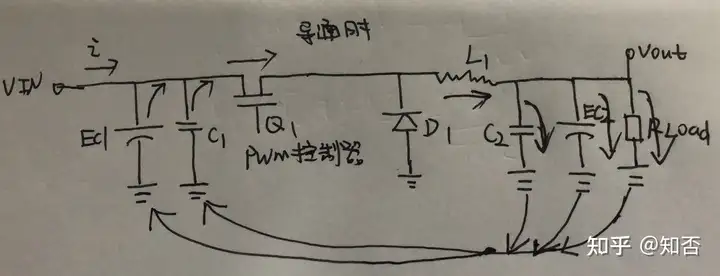

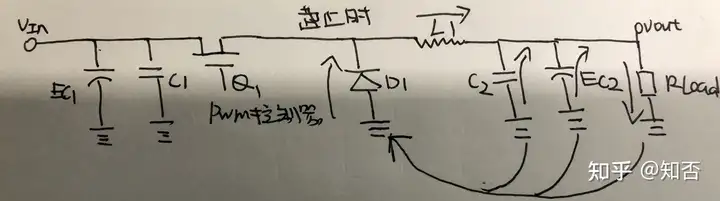

2,通过Q1的关断的电流流向图在Q1导通的时候,输入电容与输出电容的地应该尽量的紧密连接在一起,才能满足回路阻抗最小,且环路辐射面积小同理,在Q1截止时,输出电容的地应该要与续流二极管的地紧密连接一起。

往往是考核PCB工程师电源设计很重要的一点,其实电源芯片的参考设计里面都会考虑到这一点但是很多硬件工程师或者LAYOUT工程师都在参考demon设计,但是不明白其中的所以然

图二 Q1导通时各元器件电流流向图

图三 Q1截止时各元器件电流流向图 3,在第二条的基础上,我们更加深入理解一下电流回路由上图可以看出EC1与EC2电解电容原理PWM控制器,C1,C2电容接近PWM控制器由于PWM开关波形频率一般在50KHZ 。

∼\sim 2MHZ之间,属于一个高频信号,对电路的阻抗和寄生电感很敏感,由于寄生参数不能避免,且滤波电容越小谐振阻抗越高,为了较少辐射以及减少纹波,PCB设计中都会有一个共识,不管输出还是输入电容,小电容都会尽量贴近电源芯片。

以上就是关于《BUCK电路设计详解与设计调试-1(buck电路原理图)》的全部内容,本文网址:https://www.7ca.cn/baike/6785.shtml,如对您有帮助可以分享给好友,谢谢。