闲谈 Vitis AI | DPU 在 UltraScale 平台下的软硬件流程 (1)(vitis 2020.2)

原标题:闲谈 Vitis AI | DPU 在 UltraScale 平台下的软硬件流程 (1)本文由开发者 陆禹帆投稿 前言本篇中,我想跳过一些细枝末节, 先简单介绍 AMD Xilinx Vitis AI 在 Zynq 这个硬件加

速平台下软硬件开发的基本思路和流程,把各个开发流程和工具分开,帮助刚刚接触Vitis/Vitis AI的同学快速找到学习和开发的方向为什么不用其他NPU平台?在使用Xilinx DPU来对我们的AI应用进行加速之前,我们应该明确一个问题: 。

为什么我们需要使用Zynq 这样一个硬件结构,而不是使用一些专用NPU芯片 (比如NV的嵌入式开发板) 来进行加速?我个人认为, FPGA最大的优势还是其对于特定应用的定制化和可重构能力(这是FPGA相对于其他类型芯片最大的不同,同时也是FPGA最具魅力的地方)。

这种特性使得我们可以集中有限的硬件资源来动态的配置各种定制化应用,实现局部的高性能,达到四两拨千斤的效果举个例子:如果我们的在运行AI算法时,如果CPU执行预处理速度太慢,我们就可以自己设计自己的专用硬件来执行缩放,裁剪和卷积操作。

如果我们的视频编解码太慢,我们也可以使用专用的IP来进行编解码同样的功能,在非FPGA的平台上使用CPU来执行时往往速度感人搭建一个AI加速系统的必要步骤正因如此,在使用 Vitis AI 的时候,我们其实是想要定制自己的硬件结构和AI模型的。

要达成这个目标,我们会有一连串的问题需要解决:1. 首先,硬件加速系统的第一步当然就是加速模块设计(verilog或者HLS),没有加速模块,那我们的硬件加速的系统就是空谈在Vitis AI中,主要是指DPU和预处理等加速模块。

这个部分的重点是 数字前端设计和算法设计2. 完成硬件设计之后,我们会遇到第二个问题,部署硬件模块与任何的SoC设计类似,如果我们想要在软件系统中正确的调度我们的子模块,我们在硬件底层就需要把合理地分配线路、内存、带宽,正确地设计时钟、地址、中断等等。

这个部分需要着重考虑的是 SoC硬件系统设计 4. 光有系统还不行,我们需要为linux下的APP提供一套环境和Standalone程序有所不同,在Linux系统中,我们通常不会在使用直接访问地址的方式来操作加速器(除非加速器的操作和地址设计非常简单)。

因此开发一个 中间层和驱动层也是有必要的在Vitis AI中,在这个部分由AMD Xilinx提供,我们在实际的流程中几乎看不到这个部分(如果你想要开发一个私有硬件加速框架,就需要考虑这部分了) 5. 当我们完成了上面所有的硬件,软件,平台和环境之后。

我们其实才到最后一步: AI应用的开发在上一步我们已经通过驱动和接口层把软件和硬件进行了隔离因此,在这个阶段我 们本质上就是在一块专用NPU芯片上开发AI程序总的来说,我们大概需要解决以下几个问题:训练模型(在模型设计阶段就需要考虑算子是否能够被硬件支持的问题)

转换模型通常加速器是不能直接运行tf之类模型的(有些平台可以直接运行,可能是由驱动中间层实现的隐式的转换,个人水平有限此处不展开了讨论),因此我们需要把AI网络转换成硬件能够运行的执行文件 其实 就是把模型转换成加速器硬件看得懂的一组操作。

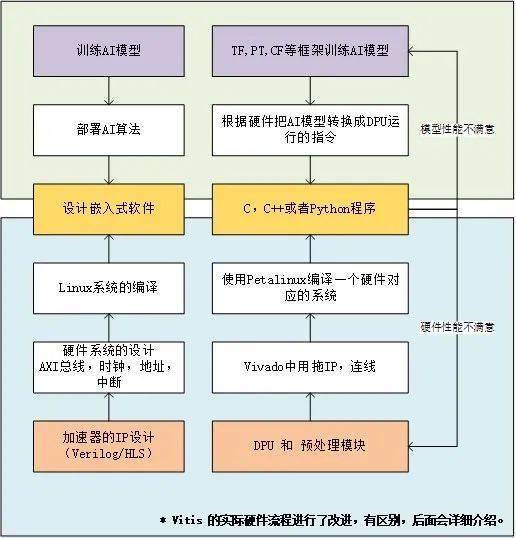

在Vitis AI 中,我们需要把tf pt等框架的模型转换成xmodel文件实现具体的加速程序,也就是在我们的程序中正确的调用各种加速器,来加速我们的APP其实我们问题总结一下,我们就得到了Vitis AI下搭建一个系统所需要的基本思路(如图所示)。

注意:此处框图列出的思路和实际的步骤有一点区别,为了大家理解我做了一点简化,此处仅仅体现我们从零开始搭建一个系统的通用思想。实际的步骤和工具的使用会在后续博客中详细的介绍。

这里其实还是需要强调下,虽然我列出了很多步骤,但是并不是说每一步都需要我们独立完成在真实的项目中,整个开发流程通常需要一个团队来完成上图是AMD Xilinx的官方的图,展示了 Vitis AI流程下需要的工程师角色和开发的方向。

这些角色的工作其实是相对独立的通常而言,我们只需要在官方工程的基础上,根据我们的需求来重新开发我们需要的部分就好例如,如果你仅需要修改AI模型,我们完全可以跳过硬件设计部分,直接使用AMD Xilinx帮我们设计好的平台。

如果你只需要改硬件,你也可以使用官方的程序,跳过AI训练的步骤关于AMD Xilinx的软件工具,开发环境下面我们来聊一聊VitisAI需要的开发工具和开发环境对于Vitis AI开发来说,我主要用到的开发工具就是 Vivado (HLS) / Petalinux / Vitis / Vitis AI。

由于工具的名字比较多,这里我把对应的工具和对应的开发方向做一个简单的介绍,方便大家快速找到自己需要的工具硬件如果你是一个传统FPGAer,那一定不需要我来介绍Vivado这个工具了Vivado作为来设计数字电路和硬件系统的专用开发工具,基本上是人手必备了。

我我唯一想要提醒的是,基于Vitis的流程来开发你的加速器时,我更推荐使用Linux开发环境,而不是Window一个经典的 Ubuntu 16.4.4 系统作为开发环境,可以节约我们很多宝贵的时间

Vivado的BlockDesign是很Vitis流程中很常用的功能之一嵌入式、硬件、软件Petalinux是 ZynqMP系列官方工程原配的系统,虽然理论上很多芯片已经可以运行Ubuntu 和 pynq,但是想要深入官方的工程,Petalinux还是不得不品尝的。

Petalinux准确的来说其实是整套Linux的开发工具,而不仅仅是单纯系统本身举个例子:在用Petalinux自动化生成设备树,一般说的是在我们的开发环境(比如Ubuntu中)使用Petalinux工具来生成。

Petalinux本身是需要安装的,也没有任何的GUI环境,因此对于新手有一定难度但是想要开发一个属于自己的动态可加载的加速应用(例如,KV260的动态加载的APP模式),Petalinux的流程是必须的。

我打算日后单独来聊一聊

Petalinux还可以配置FPGA特定的功能和应用由于名字类似,Vitis 和 Vitis AI 恐怕最最令人迷惑的两个工具了实际上,这两个工具是两个完全不同的东西Vitis 其实是一个集成开发环境,有安装包,有GUI,它和Vivado有点类似(这个软件改名叫Vitis SDK或许更合适)。

在目前的流程中,Vitis主要用来开发嵌入式程序(C)和集成加速器(Verilog/HLS)后面这部分似乎与Vivado类似,在Vitis中加入这部分的原因,主要是考虑到,Vivado不能很方便的进行软件联调。

参考上面的流程图,实际设计中我们如果完成嵌入式软件后想要修改硬件,就需要返回到Vivado中重新设计,重新使用Petalinux工具编译,最后修改软件这个流程经过好几个软件,可以说非常痛苦的Vitis的流程很好的解决这个问题。

在Vitis中,我们可以很方便的重新连接IP端口,修改IP数量硬件的编译,系统的修改,都可以由Vitis自动完成(其实Vitis在后台调用的还是Vivado的命令)当然,Vitis会限制我们对于硬件平台的修改,也不能完整编译Petalinux,因此具体流程中我们需要三个软件配合才能让其流畅的工作。

具体的流程,我会在后续的博客中具体的分析

Vitis有不少老工具的既视感AI最后让我们来谈谈Vitis AI如果你不知道Vitis AI是什么,请记住,其实Vitis AI不是一个软件而是一套给 AI开发者的工具脚本环境样例的集合像所有的github项目一样,Vitis AI不需要安装,下载Vitis AI只需要找到项目地址,然后根据README下载和配置即可。

假设你是一个纯AI的开发者想要玩Vitis AI,其实你并不需要去管Vivado、petalinux、Vitis这种工具因为AI几乎是一个纯软件的部分如果你只是先要运行一个基本的demo,你需要做的只是找到Vitis AI项目地址,clone,然后打开Vitis AI 的toturial。

至于嵌入式系统,加速器硬件,你只需要下载一个官方编译好的系统,烧录进SD卡,最后打开开发板你就会发现,系统,环境,加速器,都已经准备好了您的开发工作仅仅就参考我上图的流程中AI的部分(嵌入式以上的部分就好)。

Vitis AI是一个Github的项目小结本篇主要是闲谈个人对于Vitis AI的整个开发流程的理解,主要是想帮助一下新手快速找到一个开发目标,不至于迷失在大量的工具的方向中后续的博客中,我会继续尝试介绍一些开发流程中的细节。

返回搜狐,查看更多责任编辑:

以上就是关于《闲谈 Vitis AI | DPU 在 UltraScale 平台下的软硬件流程 (1)(vitis 2020.2)》的全部内容,本文网址:https://www.7ca.cn/baike/3512.shtml,如对您有帮助可以分享给好友,谢谢。